AMD拿下台积电2nm制程首发 台积电的N2制程工艺有什么特点

AMD拿下台积电2nm制程首发 台积电的N2制程工艺有什么特点台积电N2制程:半导体工艺的革命性跨越

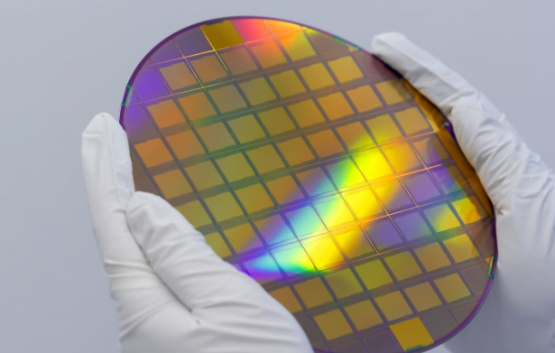

2025年4月15日,AMD宣布代号“Venice”的第六代EPYC处理器完成投片,成为全球首个采用台积电2nm(N2)制程的高性能计算(HPC)芯片。这一突破不仅终结了苹果长期垄断台积电最新工艺首发的历史,更标志着半导体技术进入全栅极(GAA)晶体管与系统级协同优化的新时代。

晶体管架构的范式跃迁

N2制程最核心的变革在于采用环绕式栅极(GAA)纳米片晶体管技术,取代沿用十余年的FinFET架构。通过垂直堆叠的纳米片通道设计,晶体管在0.5V至0.6V低电压区间实现性能飞跃——相较前代3nm工艺,相同功耗下性能提升15%,或相同性能下功耗降低24%-35%。这种能效突破得益于纳米片厚度的精确控制(优化至3-5个原子层)、掺杂剂活化效率提升,以及应力工程的创新应用。台积电数据显示,N型晶体管驱动电流提升70%,P型更实现110%的飞跃。AMD拿下台积电2nm制程首发 台积电的N2制程工艺有什么特点

设计协同优化的多维创新

N2 NanoFlex技术重新定义了芯片设计规则。通过动态调整纳米片宽度(6-50nm范围),设计者可灵活平衡性能与功耗:短单元(12-track)实现逻辑密度最大化,高单元(9-track)则专注性能突破。配合跨200mV电压范围的六档阈值电压(6-Vt)调节,芯片能在AI训练、边缘计算等不同场景中自适应优化。这种设计自由度使SRAM密度创下38Mb/mm²新纪录,较3nm工艺提升15%,同时HBM存储器的瞬态电压降(Voltage Droop)减少20%。

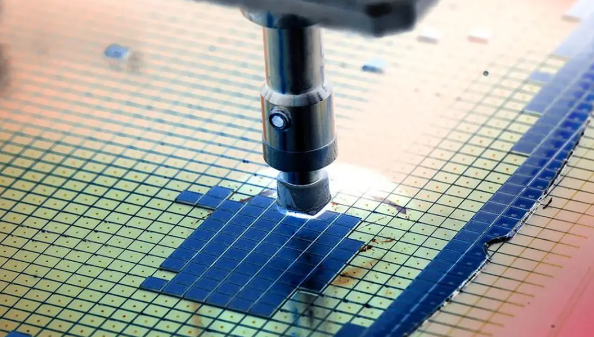

制造工艺的极限突破

N2制程在互连技术上实现双重跨越:前端引入无阻挡层钨导线,垂直栅极接触电阻降低55%;后端采用单次极紫外光刻(1P1E)蚀刻第一金属层(M1),使标准单元电容减少10%。超高性能MiM(SHP-MiM)电容器的集成,将电容密度推至200fF/mm²,为数据中心芯片提供稳定的高频供电。良率控制方面,台积电在IEDM 2024披露的早期良率已超60%,远超行业对先进节点的预期。AMD拿下台积电2nm制程首发 台积电的N2制程工艺有什么特点

产业链协同的生态重构

AMD与台积电的深度绑定在此次合作中体现得淋漓尽致。双方提前两年启动架构与制程的联合优化,使Venice处理器的晶体管密度较传统设计提升1.15倍。供应链布局更显战略眼光:亚利桑那Fab 21工厂的启用,既满足美国《芯片法案》的产能本土化要求,又通过4.5μm间距的铜RDL技术实现3D堆叠封装,为未来Chiplet架构铺路。这种“制程+封装+地缘”的三维协同,使AMD在数据中心处理器市场的制程优势扩大至两代以上。

未来计算的能效革命

N2制程的商用化将重塑算力经济模型。以Venice处理器为例,其128核设计在AI推理任务中的能效比预计提升40%,单机架算力密度可达上一代的3倍。这种进步直接推动超大规模数据中心向液冷架构加速转型,同时使边缘计算设备的续航能力突破48小时门槛。台积电规划中的N2P增强版(2026年量产)将进一步优化5%性能,为量子计算控制芯片等前沿领域提供支撑。AMD拿下台积电2nm制程首发 台积电的N2制程工艺有什么特点

从AMD的弯道超车到台积电的技术霸权,N2制程的突破不仅是摩尔定律的延续,更是半导体产业竞争规则的重写。当GAA晶体管的光芒照亮HPC与AI的算力深渊,这场由2nm工艺引发的变革,正在重新定义人类与机器的协作边界。正如台积电总裁魏哲家所言:“N2不是终点,而是通向原子级制造的新起点。”

- 戴尔科技外设产品简化升级,助力企业迈向AI PC新时代 2025-04-19

- 天阔W50荣获红点奖!你关心的都在这里 2025-04-19

- 优刻得首批接入智谱GLM Z1系列推理模型 2025-04-19

- 中国转向加拿大采购原油 中国从美国进口的原油数量骤降至每月300万桶 2025-04-19

- MAXHUB全新一代AI+电脑发布,打造AI全场景生产力新利器 2025-04-19

- 工伤保险跨省异地就医直接结算全面实施 我国医保异地结算推广进展如何 2025-04-18

- 央视董倩专访汉氏联合韩忠朝院士:干细胞技术如何普惠千万家庭 2025-04-18

- 资深公关人韩鹏出任联想中国区战略公关总监 2025-04-18